# RB/II Review

June 1970 Volume 31 No. 2

RG 174-250 GIFT OF Lohnes and Culver

TO THE BROADCAST PIONEERS LIBRARY 1771 N STREET, N.W., WASHINGTON, D. C. 20036

10/13/88

RCA Review, published quarterly in March, June, September, and December by RCA Research and Engineering, RCA Corporation, Princeton, New Jersey 08540. Entered as second class matter July 3, 1950 under the Act of March 3, 1879. Second-class postage paid at Princeton, New Jersey, and at additional malling offices. Subscription price in the United States and Canada: one year \$4.00, two years \$7.00, three years \$9.00; in other countries, one year \$4.40, two years \$7.80, three years \$10.20. Single copies up to five years old \$2.00. For copies more than live years old, contact Waiter J. Johnson, Inc., 111 Fifth Ave., New York, N. Y. 10003.

A technical journal published quarterly by RCA Research and Engineering in cooperation with the subsidiaries and divisions of RCA.

# **New Process Technologies**

for Microelectronics

# EOHNES AND CULVER

June 1970 Volume 31 Number 2

#### **New Process Technologies for Microelectronics**

Guest Editor, J. A. Amick

#### 185 Foreword

P. Rappaport and J. A. Amick

#### Aqueous Etching and Cleaning Techniques for Silicon

187 Cleaning Solutions Based on Hydrogen Peroxide for Use in Silicon Semiconductor Technology

W. Kern and D. Puotinen

- 207 Radiochemical Study of Surface Contamination I. Adsorption of Reagent Components Werner Kern

- 234 Radiochemical Study of Surface Contamination II. Deposition of Trace Impurities on Silicon and Silica Werner Kern

- 265 A New Technique for Etch Thinning Silicon Wafers A. I. Stoller, R. F. Speers, and S. Opresko

- 271 The Etching of Deep Vertical-Walled Patterns in Silicon A. I. Stoller

#### **Techniques for Metallizing Devices**

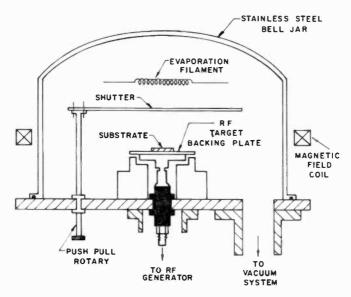

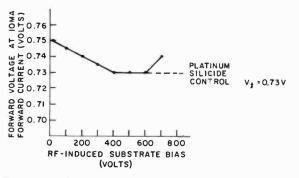

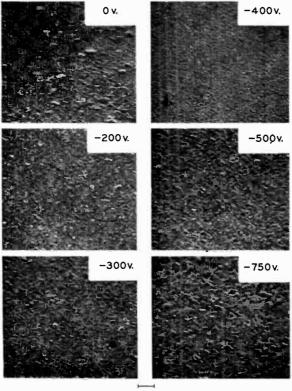

- 276 Evaporation of Aluminum with RF-Induced Substrate Bias J. L. Vossen and J. J. O'Neill, Jr.

- 293 Back Scattering of Material Emitted from RF-Sputtering Targets J. L. Vossen, J. J. O'Neill, Jr., K. M. Finlayson and L. J. Royer

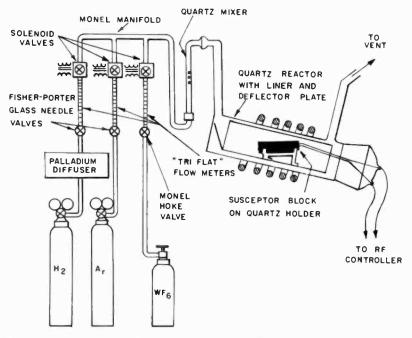

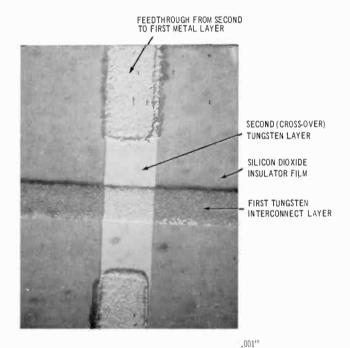

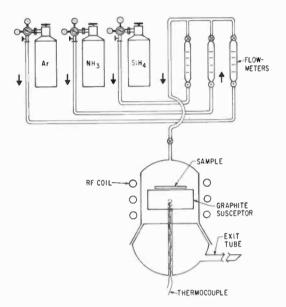

- 306 Vapor Deposited Tungsten as a Metallization and Interconnection Material for Silicon Devices

J. M. Shaw and J. A. Amick

317 Two Room-Temperature Electroless Nickel Plating Baths N. Feldstein

#### **New Process Technologies for Microelectronics**

#### **MOS Device Processing**

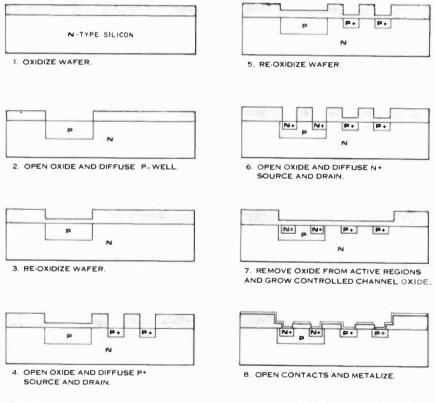

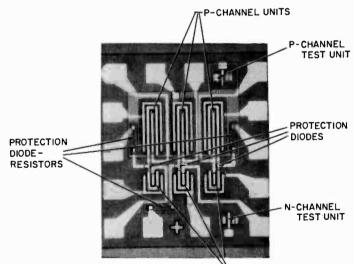

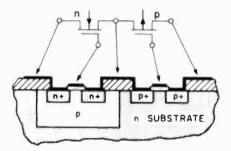

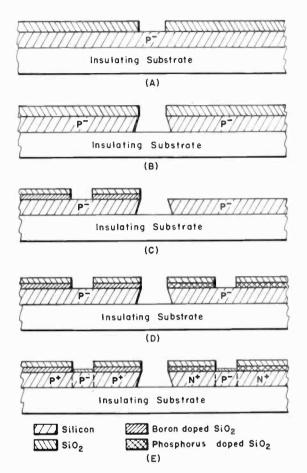

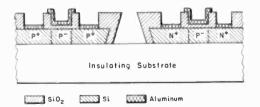

- Fabrication of Al<sub>2</sub>O<sub>3</sub> COS/MOS Integrated Circuits

F. B. Micheletti, P. E. Norris, and K. H. ZalnInger

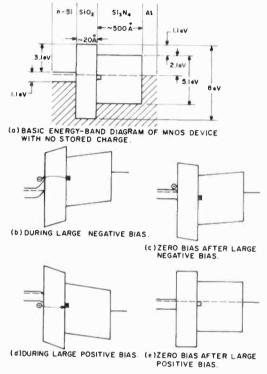

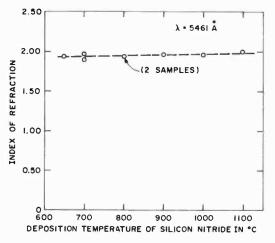

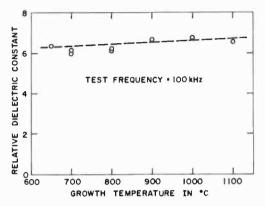

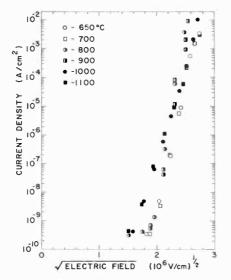

- 342 Optimization of Charge Storage in the MNOS Memory Device A. M. Goodman, E. C. Ross, and M. T. Duffy

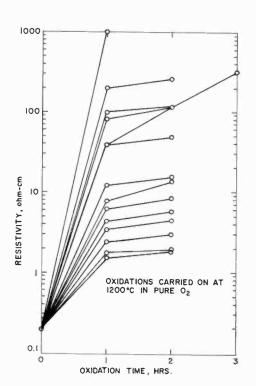

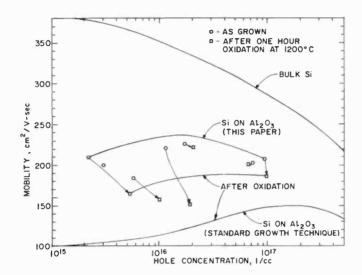

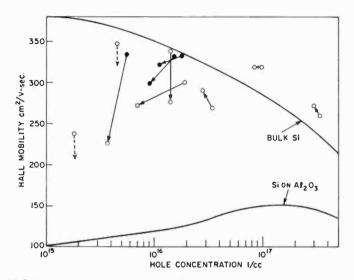

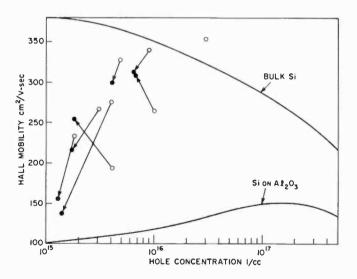

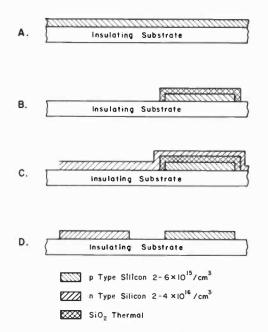

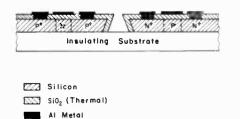

- The Epitaxial Growth of Silicon on Sapphire and Spinel Substrates: Suppression of Changes in the Film Properties During Device Processing

G. W. Cullen, G. E. Gottlieb, and C. C. Wang

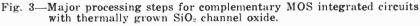

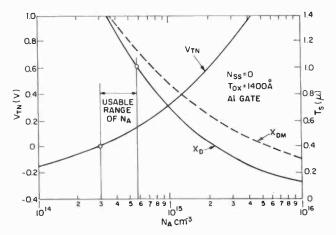

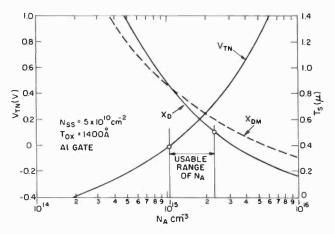

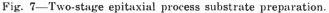

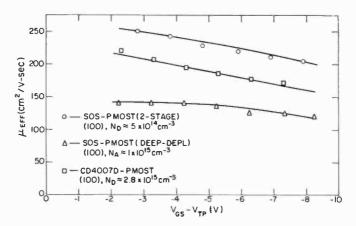

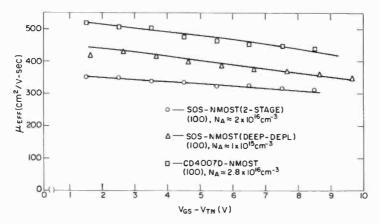

- The Performance of Complementary MOS Transistors on Insulating Substrates

E. J. Boleky

#### **Process Control and Defect Characterization**

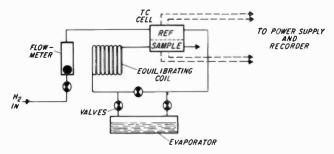

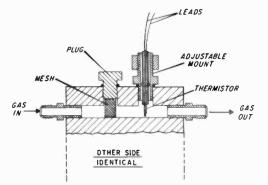

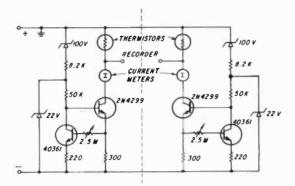

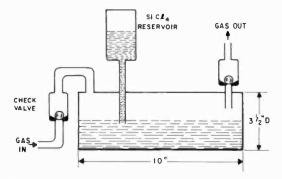

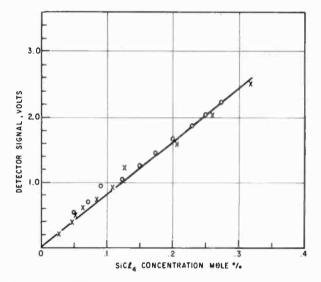

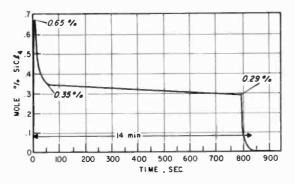

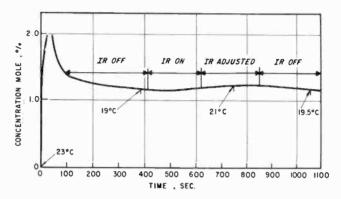

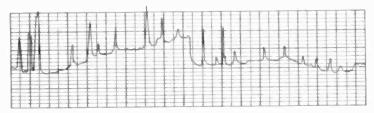

396 Monitoring Silicon Tetrachloride Concentration in Hydrogen Carrier Gas

G. A. Riley and J. A. Amick

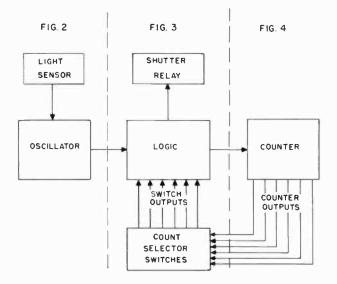

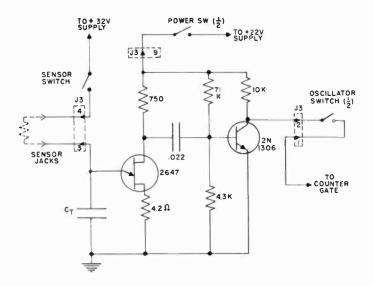

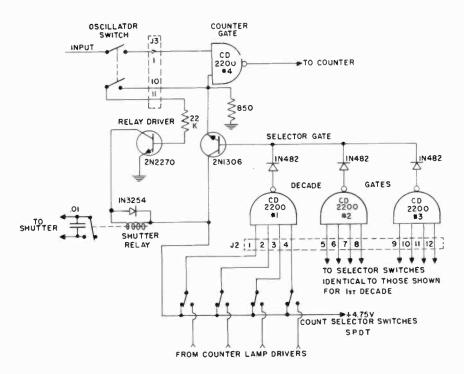

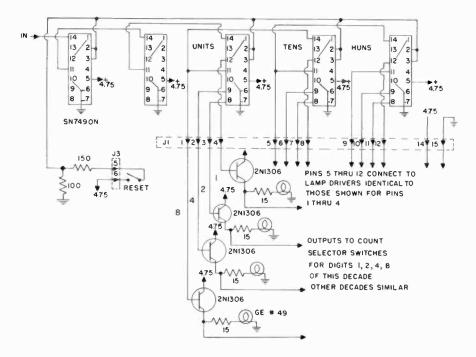

- 407 An Inexpensive Integrating Photoresist Exposure Control System G. A. Riley

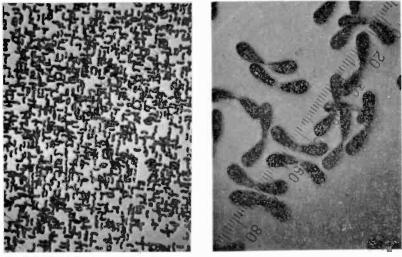

- 414 Detection of Damage on Silicon Surfaces: Origin and Propagation of Defects

A. Mayer

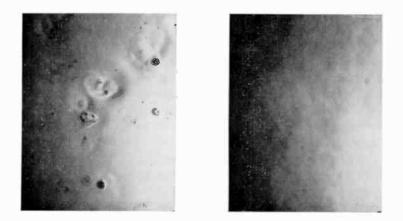

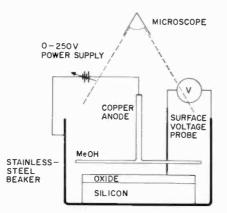

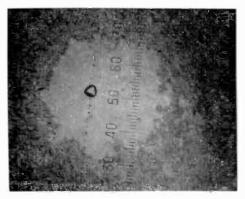

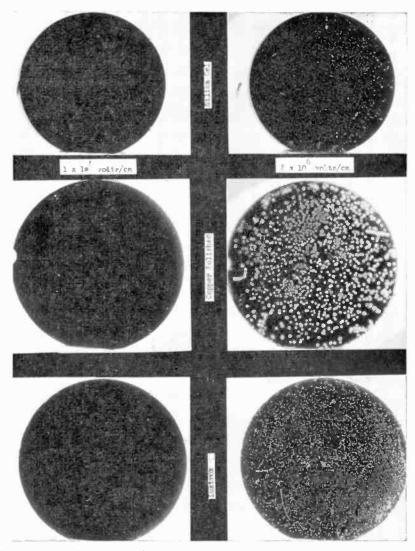

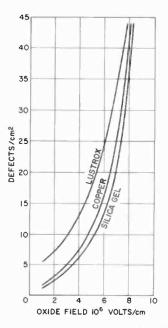

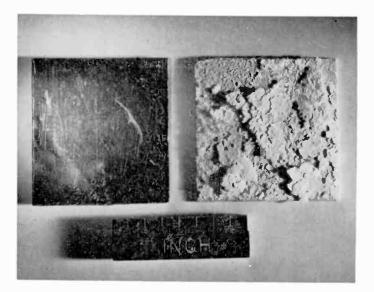

A Study of Dielectric Defect Detection by Decoration with Copper

W. J. Shannon

#### **Special Technologies**

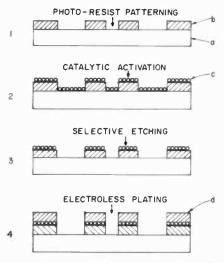

439 Selective Electroless Plating By Selective Deactivation

N. Feldstein and T. S. Lancsek

443 A Novel Technique for Forming Glass-to-Metal Seals Using a Silicon Nitride Interface Layer

A. I. Stoller, W. C. Schilp, Jr. and J. Benbenek

- 450 RCA Technical Papers

- 452 Patents

- 455 Authors

#### **RCA** Corporation

Robert W. Sarnoff Chairman of the Board and President Elmer W. Engstrom Chairman of the Executive Committee of the Board

#### **Editorial Advisory Board**

- Chairman, J. A. Rajchman RCA Laboratories

- E. D. Becken RCA Communications

- G. H. Brown RCA Patents and Licensing

- G. D. Cody RCA Laboratories

- A. L. Conrad RCA Services

- H. L. Cooke, RCA Research and Engineering

- A. N. Goldsmith Honorary Vice President, RCA

- N. L. Gordon RCA Laboratories

- G. B. Herzog RCA Laboratories

- J. Hillier RCA Research and Engineering

- E. O. Johnson RCA Solid-State Division

- H. W. Leverenz RCA Patents and Licensing

- D. S. McCoy RCA Laboratories

- L. S. Nergaard RCA Laboratories

- H. F. Olson RCA Laboratories

- K. H. Powers RCA Laboratories

- P. Rappaport RCA Laboratories

- F. D. Rosi RCA Laboratories

- L. A. Shotliff RCA International Licensing

- T. O. Stanley RCA Laboratories

- J. J. Tietjen RCA Laboratories

- W. M. Webster RCA Laboratories

- L. R. Weisberg RCA Laboratories

Secretary, Charles C. Foster RCA Research and Engineering

Editor Ralph F. Ciafone

#### **Associate Editors**

- W. A. Chisholm RCA Limited

- D. B. Dobson Aerospace System Division

- M. G. Gander RCA Service Company

- J. Gold Graphic Systems Division

- T. G. Greene Missile and Surface Radar Division

- W. O. Hadlock RCA Research and Engineering

- W. A. Howard National Broadcasting System

- C. Hoyt Consumer Electronic Systems Division

- C. A. Meyer RCA Electronic Components

- M. G. Pietz Defense Engineering

- D. R. Pratt Commercial Electronic Systems Division

- C. W. Sall RCA Laboratories

- I. M. Seideman Astro-Electronics Division

© RCA Corporation 1970 All Rights Reserved Printed in USA

### **New Process Technologies for Microelectronics**

#### Foreword

Silicon is the touchstone of modern solid state technology, and an amazing diversity of devices and monolithic circuits has been fashioned of this elemental semiconductor. In large measure this variety stems from the *electrical* characteristics of silicon. Of equal importance, silicon is adaptable to a multiplicity of handling and processing techniques because of its unique *chemical* and *physical* properties. Good as present day processes are, improvements are constantly being sought. In fact, the devising and refining of novel methods for processing silicon is a major focus of contemporary solid-state research.

In December 1968, a special issue of the RCA Review devoted to new process technologies for microelectronics appeared. This second issue on the same topic is essentially a "continuation-in-part" that describes a number of additional technologies applicable to silicon processing. The majority of the articles are derived from research carried out in the Process and Applied Materials Research Laboratory of the David Sarnoff Research Center at RCA. Contributions by the Materials Research Laboratory and the Digital Systems Laboratory as well as two from the Solid State Division of RCA round out the issue.

The papers are arranged in the following order. First, a series of five papers dealing with aqueous etching and cleaning techniques for silicon is presented. These include discussions of the contamination of semiconductor surfaces by ionic impurities in common aqueous reagents, and methods of removing these contaminants. Also, the etching of vertical-wall grooves in silicon and the uniform thinning of silicon wafers by chemical etching is described. The next group of four papers involves a variety of techniques for metallizing devices. The processes employed are sputtering-evaporation, chemical vapor deposition, and electroless deposition from aqueous solution; the materials employed are, respectively, aluminum, tungsten, and nickel. The next series of three papers discuss MOS device processing. These include papers on new technology for preparing MOS and MNOS arrays, and recent advances in silicon-on-sapphire device preparation. A group of four articles on process control and defect characterization includes a monitoring technique for improved control of the epitaxial growth of silicon, a new integrating light-flux meter, and methods for identifying imperfections in silicon and silicon dioxide layers. The issue concludes with two papers on special technologies, one concerns selective electroless plating from aqueous media and the other, a spinoff from silicon processing, describes glass-to-metal seals made possible by the use of a silicon nitride barrier layer.

The processing techniques described in these 19 papers are drawn from the classical disciplines of chemistry, physics, ceramics, metallurgy and electrical engineering. The contributions of each discipline are so commingled, however, that the processes may more aptly be described as derived from materials science. Though trained in one or another of the classical sciences, the authors have acquired broadened perspective by interacting with individuals representing other disciplines. The stimulation resulting from this contact leads to increased ingenuity and imagination in the solution of scientific problems, and is a principal factor in the development of the new technology that continues to revolutionize the electronics industry.

P. Rappaport, Director Process and Materials Applied Research Laboratory

J. A. Amick, Head Process Research

# Cleaning Solutions Based on Hydrogen Peroxide for use in Silicon Semiconductor Technology

#### Werner Kern

RCA Laboratories, Princeton, N. J.

#### David A. Puotinen

RCA Solid-State Division, Somerville, N. J.

Abstract—Hydrogen peroxide solutions at high pH are particularly effective for removing organic contaminants by oxidation; at low pH they are effective for desorbing metal contaminants primarily by complexing. The stability of these mixtures during usage and the effects of hydrogen peroxide depletion on the etching of silicon were measured as functions of resistivity type and doping concentration. These solutions are effective and simple to use, and have wide applications to the cleaning and preparation of silicon device wafers, quartz tubes, and implements employed in semiconductor processing.

#### 1. Introduction

The increased demands on performance and reliability of silicon semiconductor devices and microcircuits in recent years have required the development of improved processing techniques. One key advance in modern solid-state technology is clean processing; contamination of sensitive device surfaces is minimized so that stability and reproducibility of device characteristics are greatly improved.

Hydrogen-peroxide-containing reagents have long been used to clean electron tube components,<sup>1</sup> but their use has not previously been described for the processing of semiconductor devices. The advantages and limitations of hydrogen-peroxide-containing solutions for silicon technology are pointed out, and their efficiency for removing contaminants has been determined by radioactive tracer<sup>2,3</sup> and MOS capacitance measurements.<sup>#</sup>

<sup>\*</sup> Parts of this work were performed and reported under U. S. Government Contract AD-36-039-SC-86729 (ref. 4).

#### 2. Types, Sources, and Effects of Surface Contaminants

Surface contaminants can be classified broadly as molecular, ionic, or atomic.

Typical molecular contaminants are natural and synthetic waxes, resins, and oils. These are typically present after the mechanical grinding, lapping, and polishing operations of wafers. They may also include grease from fingers and greasy films that are deposited when surfaces are exposed to room air or stored in plastic containers. Photoresists and organic solvent residues also fall into this category. Layers of such molecular impurities in contact with the substrate surface are usually held by weak electrostatic forces. Organic contaminants on silicon devices, especially on surface-sensitive MOS structures, may cause polarization<sup>5</sup> and ionic drift<sup>6</sup> due to the transport of protons.<sup>7</sup> Water-insoluble organic compounds tend to make semiconductor and oxide surfaces hydrophobic, thus preventing the effective removal of adsorbed ionic or metallic impurities. The elimination of molecular contaminants should therefore be considered the first step in a cleaning process.

Ionic contaminants are present after etching of wafers in HFcontaining etchants or in caustic solutions, even after extensive rinsing in deionized water.<sup>2</sup> They may deposit on the silicon surface by physical adsorption or by chemisorption. The removal of chemisorbed ions is much more difficult than the removal of ions attached to the surface by physical forces, and a chemical reaction must generally be used to achieve desorption. Of the ionic contaminants, alkali ions are particularly harmful in that they may move under the influence of electric fields or at elevated temperatures, causing inversion layers, surface leakage, drifts during device operation, and other instabilities.<sup>8</sup> In the growth of epitaxial silicon layers, visible ionic and molecular residues from improper cleaning are reported to give rise to twinning, dislocations, stacking faults, and other crystal defects.<sup>9</sup>

Atomic contaminants present on silicon surfaces include heavy metals such as gold, silver, and copper. They originate from acid silicon etchants and are usually plated out in the form of metallic deposits.<sup>3</sup> The removal of this type of contaminant generally requires reactive agents that dissolve the metal and complex the ionic form to prevent redeposition from the solution. Atomic impurities, especially the heavy metals, can seriously affect minority-carrier lifetime, surface conduction, and other device parameters governing stability of the devices.<sup>10-12</sup>

Since a contaminated surface is likely to contain all three types of impurities, it is necessary to first remove the gross organic residues

CLEANING SOLUTIONS

masking the surface, then the residual organic materials, and finally the residual ionic and atomic contaminants. The gross organic residues from materials used in wafer-polishing operations may be removed by treatment with an organic solvent.\*

#### 3. New Cleaning Procedure

Two solutions, used sequentially, have been devised to remove any organic and inorganic contaminants remaining after solvent rinsing. Both solutions contain volatile reagents diluted with pure water. The exact compositions are not critical; some of the work discussed was done using slightly different compositions. However, the recommended compositions afford greater freedom in their application.

The first solution, typically 5-1-1 to 7-2-1 parts by volume of  $H_2O^*-H_2O_2^{\dagger}-NH_4OH^{\ddagger}$ , was designed to remove organic contaminants that are attacked by both the solvating action of the ammonium hydroxide and the powerful oxidizing action of the peroxide. The ammonium hydroxide also serves to complex some group I and II metals such as Cu, Ag, Ni, Co and Cd.

The second solution consist of  $H_2O^*-H_2O_2^{\dagger}-HCl^{\dagger\dagger}$  in the typical proportions 6-1-1 to 8-2-1 by volume and was chosen to remove heavy metals and to prevent displacement replating from solution by forming soluble complexes with the resulting ions. The reagents used in these two solutions were chosen over other possible combinations because they are completely volatile. The cleaning action of the dilute  $HCl-H_2O_2$ solution is similar to that of concentrated  $H_2SO_4$ - $H_2O_2$ , or that of chromic-sulfuric acid mixtures, but is not as hazardous and presents no disposal problems.

<sup>\*</sup> Rinses in hot trichloroethylene are most generally used and yield satisfactory results if overheating is avoided so that thermal decomposition of the solvent is minimized. Triethyl amine is commonly added to trichloroethylene as a stabilizer, i.e., it reacts with the hydrochloric acid formed by thermal decomposition of the solvent. The resultant triethyl amine hydrochloride may remain as a residue on the surface following a rinse in trichloroethylene. As much as 140 mg of residue has been isolated from 1000 ml of a typical batch of electronic grade trichloroethylene. Tetrachloroethylene stabilized with ethyl alcohol does not have this disadvantage and is a more effective degreasing solvent. Hot xylene is one of the most effective degreasing solvents; even halocarbon grease residues are readily removed from silicon wafers. However, it has the disadvantage of being flammable and toxic. Freon fluorocarbon solvents are also satisfactory, especially if vapor degreasing or carefully controlled ultrasonic agitation techniques are employed.

<sup>\*</sup> filtered DI or quartz distilled  $H_2O$

<sup>† 30%</sup> unstabilized H2O2

<sup>‡27%</sup> NH.OH

<sup>†† 37%</sup> HCl

The hydrogen peroxide used in the cleaning solutions should be the unstabilized, electronic grade. Stabilized peroxide may contain nonvolatile sodium phosphate and sodium stannate or amine derivatives as stabilizers. As mentioned, the compositions are not critical but the solutions of the approximate proportions given above have been found to be reliable, as well as simple to prepare and use.

Cleaning in either mixture is carried out at  $75^{\circ}$ C to  $85^{\circ}$ C for time periods of 10 minutes to 20 minutes, followed by a quench and rinse in running DI or quartz distilled water. As a final step, the wafers are "spun" dry and immediately transferred to an enclosure flushed with prefiltered inert gas. *Caution*: As both solutions are vigorous oxidizing agents and can evolve large quantities of gas even when cold, they must be kept in vented containers, or, preferably, mixed just before use.

#### 4. Effectiveness of Contaminant Removal

Mechanically polished and precleaned bare and thermally oxidized silicon wafers were deliberately contaminated with typical organic waterinsoluble materials, such as Apiezon wax, stearic acid, etc. They were rinsed with organic solvents and then cleaned with the ammoniahydrogen peroxide solution only. Water spray tests<sup>13</sup> indicated that less than 1/10 monomolecular layer of hydrophobic organic contaminant remained.

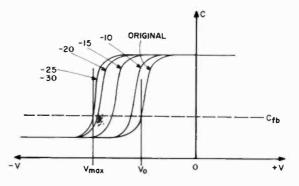

The presence of surface contaminants, including water soluble organic compounds that can not be detected by the water spray test, can be determined by the more sensitive Capacitance-Voltage Bias Temperature Test (CVBT) on Metal-Oxide-Semiconductor (MOS) capacitors. \* 8, 14, 15 The capacitor is formed by thermally growing a thin oxide layer on a silicon wafer to be tested, then evaporating a metal contact. The CVBT characteristics of the capacitor are measured in an inert atmosphere using a biasing stress of  $10^6$  V/cm and a bias temperature of 300°C. The lateral displacement of the characteristic CV curve provides a measure of the mobile charge (a shift of 1.0 volt is equivalent to  $2.1 \times 10^{11}$  mobile charges/cm<sup>2</sup> for an SiO<sub>2</sub> thickness of 1000Å). The use of MOS capacitors as detectors for both organic and inorganic contaminants is fully established<sup>7, 14, 15</sup> by correlation of CV measurements with radiotracer analysis of deliberately contaminated MOS devices. The CVBT method as described was therefore utilized to test the effectiveness of our cleaning procedure for removing deliberately

<sup>\*</sup> For example, Hofstein<sup>7,14</sup> demonstrated by CVBT techniques that contamination of MOS devices with alcohols can cause proton drift instability. Similar drifts caused by other organic contaminants were also observed by CVBT tests.<sup>6</sup>

introduced organic contaminants on MOS devices. These results are summarized in Section 5.

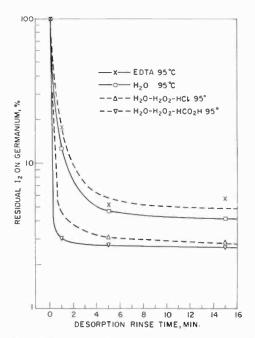

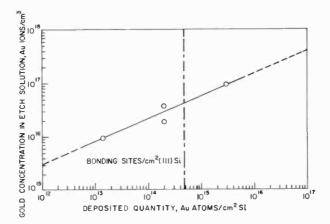

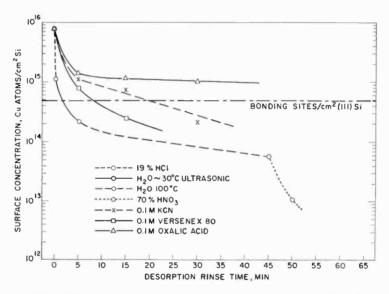

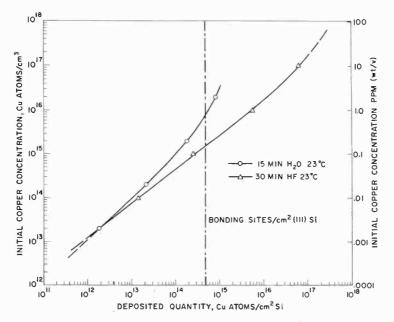

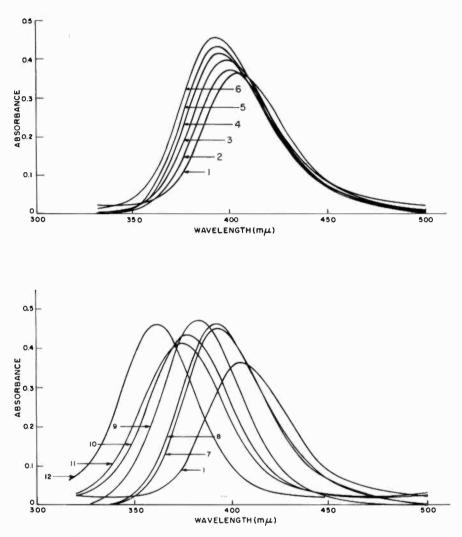

For inorganic contamination studies, silicon wafers and fused quartz samples were immersed in various solutions or etchants containing known quantities of specific ionic impurities "labeled" with radioactive ions of the same type. The quantities of radioactive impurities deposited and the amounts subsequently removed by cleaning treatments were determined by monitoring the radioactivity.<sup>2,3</sup> The efficiency of various acid hydrogen peroxide solutions for removing atomic contaminants including copper, gold, and chromium from silicon wafers and quartz surfaces is illustrated by the desorption curves presented in Figs. 1-4. For comparison, rinse curves for water, diluted hydrogen peroxide without acid, and diluted acid without hydrogen peroxide are also shown. These data were obtained by gamma-radioactivity measurements using Au<sup>198</sup>, Cu<sup>64</sup>, and Cr<sup>51</sup> as radioactive tracers.

Curve A in Fig. 1 shows the results obtained with silicon waters that had been etched in a HNO<sub>3</sub>-HF mixture containing Au<sup>198</sup>. The surface concentration on the etched silicon after quenching with deionized water followed by a 30-second water rinse was  $7.3 \times 10^{13}$  Au atoms/cm<sup>2</sup>. Desorption at 90°C with an HCl-H<sub>2</sub>O<sub>2</sub>-H<sub>2</sub>O mixture removed 97.4% of the gold in 15 minutes. For comparison, a solution consisting of 1 vol HCO<sub>2</sub>H (formic acid),<sup>\*\*\*</sup> 1 vol 30% H<sub>2</sub>O<sub>2</sub>, and 8 vol distilled H<sub>2</sub>O removed 86% of the gold in the same time period. Used separately, the reagent components (diluted H<sub>2</sub>O<sub>2</sub>, diluted HCO<sub>2</sub>H, distilled H<sub>2</sub>O) removed only negligible quantities of the gold.

Silicon immersed in diluted HF had initially  $2 \times 10^{15}$  Au atoms/cm<sup>2</sup>. After 15 minutes desorption in HCl-H<sub>2</sub>O<sub>2</sub>-H<sub>2</sub>O, similar percentages of gold removed were found as for acid-etched silicon (Curve B, Fig. 1). Curve C in Fig. 1 shows the desorption for silicon previously etched in iodine-containing HF-HNO<sub>3</sub> etchant, resulting in an initial gold surface concentration of  $3 \times 10^{15}$  atoms/cm<sup>2</sup>. In this case, the formic acidhydrogen peroxide was more effective (98.8% removal) than the HCl-H<sub>2</sub>O<sub>2</sub>-H<sub>2</sub>O mixture.

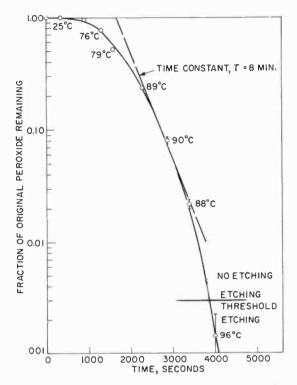

Fused quartz contaminated with Au<sup>198</sup> from HNO<sub>3</sub>, HCl, HF, and aqua regia, to an initial surface concentration of  $10^{11}$  to  $10^{12}$  Au atoms/cm<sup>2</sup> was decontaminated effectively with acid H<sub>2</sub>O<sub>2</sub>. A typical desorption curve is presented in Fig. 2. Similar results were obtained with quartz that had been immersed in the same acids but contained Cu<sup>64</sup>.

<sup>\*\*</sup> Formic acid can be used<sup>3</sup> instead of hydrochloric acid to lower the pH of the solution to attain metal complexing action; however, this system is generally less effective, partly because of consumption of hydrogen peroxide in the oxidative breakdown of the formic acid.

As seen from Fig. 3, acid hydrogen peroxide is very effective for desorbing copper from silicon. Over 99% is removed within the first 2 minutes of rinsing. Over 30 different desorption treatments involving combinations of complexing, chelating, and oxidizing agents have been tested for copper removal.<sup>3</sup> None was as effective as the acidic hydrogen peroxide. Water or hydrogen peroxide without added acid were quite ineffective.

#### Substrates:

Curve A (dotted line)—Si etched in  $HNO_s + HF + Au^{108}$ ; 100% =  $7.3 \times 10^{13}$  Au atoms/cm<sup>2</sup>

Curve B (solid line)—Si immersed in 49% HF + Au<sup>198</sup>; 100% = 2.2  $\times 10^{15}$  Au atoms/cm<sup>2</sup>

Curve C—(dashed line)—Si etched in  $HF + HNO_3 + I_2 + CH_3CO_2H + Au^{198}$ ; 100% =  $3.0 \times 10^{15}$  Au atoms/cm<sup>2</sup>

#### Solutions:

- $\times$  Deionized and distilled H<sub>2</sub>O, 100°C

- $\nabla$  1 vol 90% HCO<sub>2</sub>H + 9 vol H<sub>2</sub>O, 90°C

- $\Box$  1 vol 30% H<sub>2</sub>O<sub>2</sub> (unstabilized) + 9 vol H<sub>2</sub>O, 90°C

- $\bigcirc 1 \ \text{vol} \ 30\% \ \text{H}_2\text{O}_2 + 1 \ \text{vol} \ 90\% \ \text{HCO}_2\text{H} + 8 \ \text{vol} \ \text{H}_2\text{O}, \ 90^\circ\text{C}$

- $\triangle$  1 vol 30% H<sub>2</sub>O<sub>2</sub> + 1 vol 1N HCl + 8 vol H<sub>2</sub>O, 90°C

- Fig. 1—Desorption efficiency for gold labeled with Au<sup>198</sup> from silicon surfaces with various solutions at 90°C.

Similar desorption curves for chromium on silicon are presented in Fig. 4. Diluted formic acid- $H_2O_2$  mixture at 90°C removed 93% of the chromium in 5 minutes. Less dilute solutions were more effective;  $HCl-H_2O_2$  was not tested, but can be expected to be even better because of the high solubility of chromium in HCl.

The desorption of sodium was previously studied with Na<sup>22</sup> and Na<sup>24</sup> as tracers for the sodium ions. Aqueous solutions containing HCl were demonstrated to be highly effective in removing physically and chemically adsorbed sodium ions from silicon surfaces.<sup>2</sup>

#### Substrates:

Fused quartz etched in 49% HF + Au<sup>198</sup>;  $100\% = 1.56\times 10^{12}$  Au atoms/cm<sup>2</sup>

#### Solutions:

- \* Deionized distilled H<sub>2</sub>O, 23°C

- $\times$  Deionized and distilled H<sub>2</sub>O, 100°C

- 1 vol 30%  $H_2O_2 + 1$  vol 1N HCl + 8 vol  $H_2O_2$ , 23°C

- $\bigcirc$  1 vol 30% H<sub>2</sub>O<sub>2</sub> + 1 vol 1N HCl + 8 vol H<sub>2</sub>O, 90°C

- Fig. 2—Desorption efficiency for gold labeled with Au<sup>198</sup> from fused quartz under various conditions.

RCA Review • June 1970 193

Considerably higher concentrations of the metals on silicon were used in these desorption studies than are normally present in silicon processing in order to determine the effectiveness of the cleaning mixtures. Although the rates of desorption are different for different metals, the following generalizations can be made on the basis of the results obtained. (1) Each of the single components ( $H_2O$ ,  $H_2O_2$ , HCl,  $HCO_2H$ ) used separately, regardless of the temperature, is relatively ineffective. (2) Elevated temperatures increase the oxidation potential of the acidic hydrogen peroxide system and the efficiency of desorption.

Radioactive-tracer studies have also demonstrated the importance of the acidic hydrogen peroxide treatment following an oxide removal step in aqueous HF or buffered HF. Heavy metal impurities are readsorbed by the silicon where it becomes exposed to these reagents, but can be effectively removed in the acid peroxide medium.

#### Substrates:

Si immersed in 49% HF + Cu<sup>64</sup>;  $100\% = 1.5 \times 10^{17}$  Cu atoms/cm<sup>2</sup> for  $\Box$ , ×,  $\odot$ ; for  $\triangle$ ,  $100\% = 3.3 \times 10^{16}$  Cu atoms/cm<sup>2</sup> Solutions:

Explanations as for Fig. 1, except that H<sub>2</sub>O temperature was 97°C

Fig. 3—Desorption efficiency for copper labeled with Cu<sup>64</sup> from silicon with various solutions at 90°C.

The behavior of a number of other metals in acidic hydrogen peroxide can be predicted from data in the literature. The following metals are known to dissolve: silver,<sup>16</sup> nickel,<sup>16</sup> cobalt,<sup>17</sup> lead,<sup>18, 19</sup> magnesium,<sup>16</sup> niobium,<sup>20</sup> tellurium,<sup>21</sup> and tungsten.<sup>16</sup>

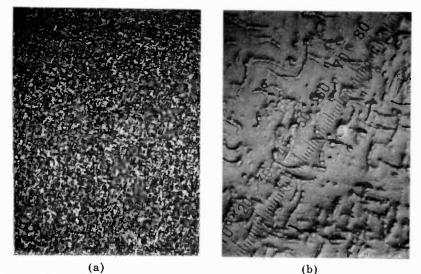

It should be noted that the cleaning solutions are effective for surface contaminants only. If the contaminant is already distributed within an oxide layer, an etch back with dilute HF followed by cleaning in the acidic hydrogen peroxide mixture may be required to remove it. In a more pragmatic sense, silicon wafers that have undergone this cleaning treatment can be used for the routine growth of silicon epitaxial layers free from hillocks, bumps, spikes, etc. Furthermore, vapordeposited SiO<sub>2</sub> layers deposit uniformly on the wafers, a fact previously correlated with surface cleanliness.<sup>22</sup>

Ellipsometry<sup>23-25</sup> was used to determine the oxide thickness of clean

#### Substrate:

Si immersed in 49% HF + Cr<sup>51</sup>;  $100\% = 2.2 \times 10^{14}$  Cr atoms/cm<sup>2</sup> Solutions:

Explanations as for Fig. 1 except that H<sub>2</sub>O temperature was 95°C.

Fig. 4—Desorption efficiency for chromium labeled with  $Cr^{51}$  from silicon at 90°C.

Si surface.\* Chemically/mechanically polished (111)-oriented silicon wafers (1-10 ohm-cm p-type) had an initial film thickness of 21 Å. After the cleaning treatment in the ammonia-hydrogen peroxide solution, the film thickness was  $18 \pm 1$  Å; this thickness changed only slightly to  $16 \pm 1$  Å on the subsequent acid-hydrogen peroxide treatment.26 It can be concluded that no excessive surface oxidation takes place during these cleaning treatments.\*\*

## 5. Experiments in the Electrical Performance of Devices

The effectiveness of the cleaning procedure was evaluated using MOS capacitors fabricated using these cleaning treatments.

CVBT tests on silicon wafers deliberately contaminated with methanol and cleaned in these solutions prior to metallization showed flatband voltages and driftable charge levels identical to those of uncontaminated control samples.27

A statistical evaluation of MOS capacitors fabricated on reference ingot wafers cleaned with these solutions was also performed using CVBT testing. Over a nine-month test period, a 1100 and a 1200°C furnace was found to result in flat-band shifts arising from driftable charge of (average  $\pm 1\sigma$  limit)  $0.20 \pm 0.07$  volt, and  $0.18 \pm 0.09$  volt, respectively.

## 6. Chemistry of Hydrogen Peroxide Solutions

#### 6.1 General

The chemistry of hydrogen peroxide has been extensively studied.<sup>16, 28, 29</sup> It is a powerful oxidizing agent in both acidic and basic solutions. Dilute solutions at 50 °C are most stable at a pH in the vicinity of 4.5 to 5.0, and are least stable at high pH's, decomposing to water and oxygen. Decomposition is catalized by traces of most heavy metals.

As cleaning agents, hot formic acid and hydrogen peroxide,<sup>1</sup> hot hydrogen peroxide and hydrochloric acid,13 and cold hydrogen peroxide and ammonium hydroxide<sup>30, 31</sup> have been used in a variety of applications. In all of these mixtures, the chemistry is considerably complicated by changes in the reagent concentration with time, and by the complexing nature of both the chloride and ammonium ions. For example, nickel and cobalt each form six different amines;32 copper and zinc also form amine complexes. The potential-pH diagram shown in

<sup>\*</sup> The refractive index of SiO<sub>2</sub> (1.48) was assumed for all films. \*\* For comparison, immersing the cleaned wafers in HF solution fol-lowed by water rinsing reduced the film thickness to  $7 \pm 1$  Å; subsequent boiling for 15 or 30 minutes in deionized and distilled water led to a limiting film thickness of  $31 \pm 1$  Å.<sup>26</sup>

CLEANING SOLUTIONS

Fig. 5 is thus highly idealized, but it illustrates the relative oxidizing powers of the cleaning solutions at room temperature. The measured pH ranges for the alkaline peroxide and acid peroxide solutions described in this paper are indicated.

Fig. 5—Potential versus pH diagram for hydrogen peroxide solutions at 25°C.

Within the limits of solution stability and peroxide depletion (Section 6.2) the exact concentrations of reagents are not critical. However, if excess peroxide is used, the solutions tend to froth and overflow the container from the too rapid evolution of oxygen.

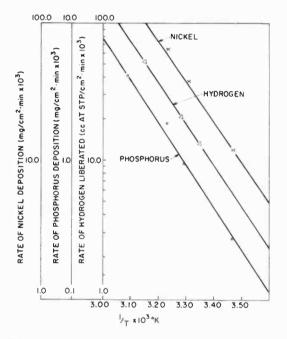

#### 6.2 Stability of Hydrogen Peroxide Mixtures

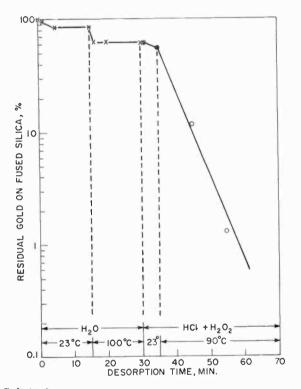

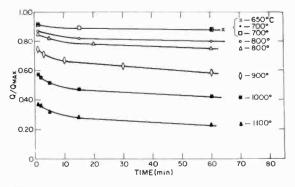

These hydrogen peroxide solutions gradually decompose, losing their cleaning effectiveness. Their decomposition rates were determined by titration with a standard potassium permanganate solution. Half-lives of the alkaline and acidic solution<sup>33</sup> at room temperature are, respectively, 11 hours and 50 hours (Fig. 6); these half-lives decrease rapidly with increasing temperature. The relative hydrogen peroxide content

of the acidic solution was found to decrease by 98% in 30 minutes, and by 99.95% in 60 minutes, after the solution reached the operating temperature of  $80^{\circ}C$ .<sup>†</sup>

Fig. 6—Rate of decomposition of acidic and alkaline hydrogen peroxide as a function of storage time at 23°C.

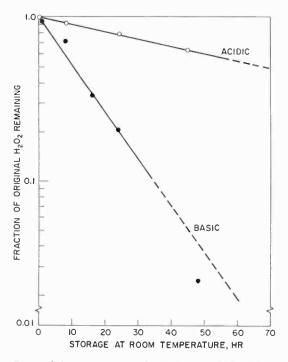

To determine more precisely the shape of the decomposition curve during typical processing conditions, the peroxide content in 405 ml of alkaline solution heated in a beaker on a hot plate was monitored. After the beaker was placed on the hotplate the amount of peroxide remaining was determined as a function of time (Fig. 7). The half-life of the solution at 88-90 °C was approximately 5 minutes, and the time for the concentration of peroxide to be reduced to the etching threshold\* level for (111)-oriented silicon was approximately 40 minutes after the solution reached temperature. Since the recommended cleaning time is 10 to 20 minutes at 75-80 °C, there is an adequate margin of safety if the initial peroxide concentration is at the recommended level.

<sup>&</sup>lt;sup>†</sup> It should be realized that the rates of decomposition can be affected by the presence of trace impurities.

<sup>\*</sup> This is the etching threshold under the conditions recommended for cleaning silicon.

Fig. 7—Fraction of hydrogen peroxide remaining as a function of use time in H<sub>2</sub>O<sub>2</sub>-NH<sub>4</sub>OH-H<sub>2</sub>O cleaning solution (etching threshold indicated by horizontal line is for (111) and (100)-oriented silicon; value is approximate).

#### 6.3 Effects of Hydrogen Peroxide Depletion

A bare silicon surface is readily attacked by even a weak base, such as ammonium hydroxide. However, when hydrogen peroxide is present, the surface is immediately passivated, presumably by the formation of a thin (<50 Å) continuous layer of hydrous oxide. This oxide layer is very resistant to chemical attack by ammonium hydroxide at the temperatures and concentrations used for cleaning.\*

The etch rate of n- and p-type (111)-oriented chemically polished silicon has been determined in hydrogen-peroxide-free ammonium hydroxide solutions. Resistivity and types used were 0.25 ohm-cm and 20 ohm-cm p-type; 1 ohm-cm and 15 ohm-cm n-type. Etching was conducted in a Pyrex chamber immersed in a constant-temperature bath

<sup>\*</sup> A complete equilibrium potential-pH diagram for the Si-H\_0 system is given in Ref. [34].

and capped with a stoppered, water-cooled condenser to minimize loss of ammonia. Wafers were prepared for etching by growing 5000 Å of oxide in steam at 1000°C, by defining and etching a 1-cm-wide stripe along a diameter to expose a bare silicon surface, and by cleaning in  $H_2O-H_2O_2-NH_4OH$  solution. Each wafer was then given a 5 second dip in 5% HF, rinsed in distilled water, quartered, and transferred to the etching apparatus. This procedure was adopted to ensure that the

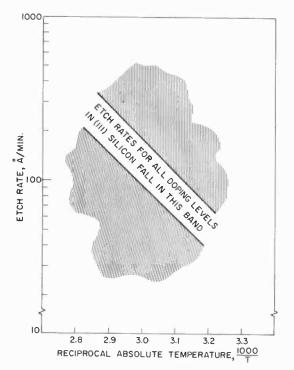

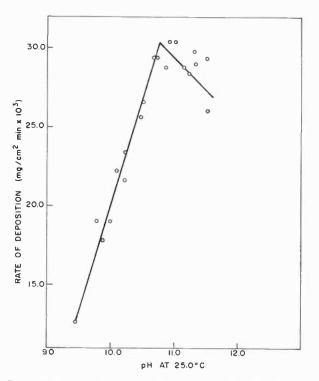

Fig. 8—Etch rate of (111)-oriented silicon in ammonium hydroxide solutions as a function of temperature.

bare silicon surface was covered by no more than a thin film of freshly formed hydrous oxide when the wafer quarters were placed in the etching solution. The samples were removed from the etch at prescribed time intervals and the oxide was stripped in buffered HF etch.

The depth of step formed in the silicon as a result of localized etching was measured with a Talysurf<sup>\*\*</sup> surface profilemeter with an accuracy of better than  $\pm 2\%$ . This technique was also used to deter-

<sup>\*\*</sup> Talysurf Model 4, Rank Taylor Hobson, Leicester, England.

mine the thickness of the oxide films by measuring the step height formed from the top of the film to the substrate surface.

The observed etch rate values for 2N to 6N NH<sub>4</sub>OH solutions fall into the broad band shown in Fig. 8 where the etch rate is plotted as a function of reciprocal temperature. Despite the precautions used to obtain an oxide-free surface, plots of step height versus time showed considerable scatter even on the four quadrants of the same wafer. These results may indicate that the oxide formed at room temperature offers some barrier to the attack of ammonium hydroxide on silicon, or that the chemical polishing had not completely removed the workdamaged surface and that the etch-rate variations reflect this. Within the limits of the experiment, there was no difference between the etch rates of n- and p-type silicon. There was no discernable etching of the oxide mask at any concentration or temperature used in this experiment. It should be noted that ammonium hydroxide etching of silicon is orientation sensitive; (100)-oriented material etches more rapidly than (111)-oriented material. As expected, no silicon etching effects have been observed in aqueous HCl or in the acidic peroxide solution.

#### 6.4 Effects Of Fluoride Ion Additive

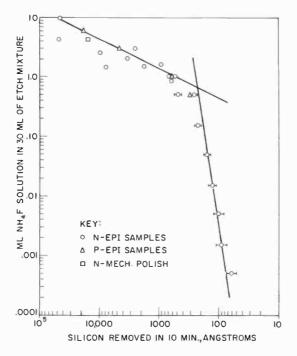

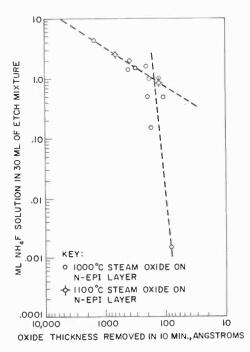

A common semiconductor processing operation is to either completely strip the surface oxide or to conduct limited etch-back in HF or buffered HF. A large number of fluoride ions are adsorbed during this kind of treatment.<sup>2</sup> If rinsing is inadequate, these fluoride ions could transfer to the ammoniacal cleaning solution producing a silicon etch.<sup>35</sup> As an extreme test of this type of contamination, the etch rates of both nand p-type (111)-oriented epitaxial silicon in H<sub>2</sub>O-NH<sub>4</sub>F-H<sub>2</sub>O<sub>2</sub> solutions were determined over a five-decade range in fluoride ion concentration. The solutions were prepared by adding aliquot amounts of aqueous ammonium fluoride solution (40% NH<sub>4</sub>F by weight) to 5 ml of 30% unstabilized  $H_2O_2$  and diluting with distilled water to a total volume of 30 ml. Each test solution was preheated on a hotplate for five minutes to bring the temperature to  $75 \pm 2^{\circ}$ C, the wafer was added, and heating continued for 10 minutes to a final temperature of 80°C. The wafer preparation procedure was similar to that described in the previous section except that the HF dip was omitted. The thickness of the remaining oxide was measured, the oxide was then stripped in buffered etch, and the silicon etch-step height was measured on the Talysurf.

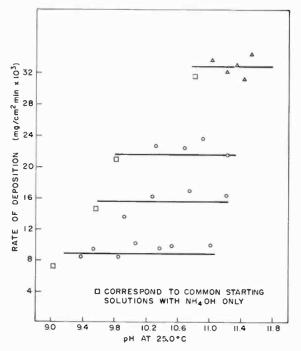

The observed variation of silicon and silicon dioxide etch rate with fluoride ion concentration are shown in Figs. 9 and 10. The silicon etch-rate curve has two distinct regions, one for low fluoride ion concentration and one at higher concentrations where the etch rate increases quite rapidly with increasing fluoride ion concentration. While the different regions are of considerable interest in the interpretation of the etching mechanism, the immediate practical significance of this curve is that peroxide solutions containing fluoride ion concentration

Fig. 9—Etch rate of (111)-oriented silicon in ammonium fluoride solutions (solution composition: 5 ml 30% H<sub>2</sub>O<sub>29</sub> aliquot 40 wt % NH<sub>4</sub>F solution, diluted with H<sub>2</sub>O to total volume of 30 ml).

at the level that might be found by casual contamination during normal handling and processing have very low etch rates. This means that trace contamination of the  $H_2O_2$ -NH<sub>4</sub>OH cleaning solutions with fluoride ion will not be a cause of etching of (111) oriented silicon wafers. A similar conclusion applies to (100) wafers. It follows that any fluoride ion that might be leached out of Teflon workholders will not cause any significant amount of etching. The oxide etch rate becomes appreciable only at the highest fluoride concentrations and is essentially zero at concentrations below 0.1 ml NH<sub>4</sub>F per 30 ml solution.

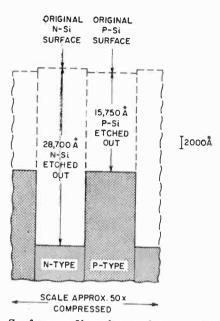

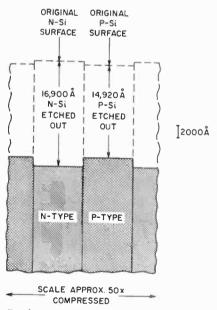

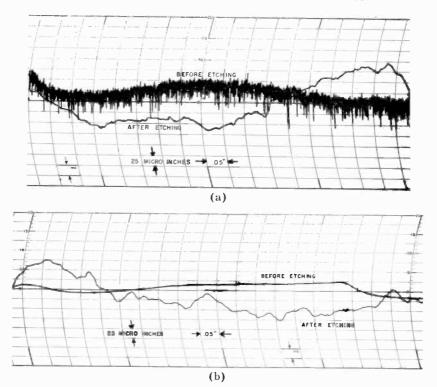

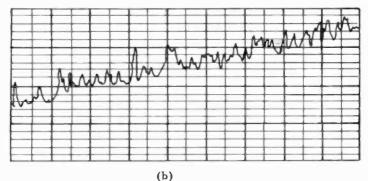

A feature of both the ammonium hydroxide and the ammonium fluoride-hydrogen-peroxide solutions is that, although physically isolated samples of n-type and p-type (111) oriented silicon will etch at nearly the same rate, adjacent n and p regions will etch at different rates. This differential etch rate may be illustrated by the change in relative heights shown in Fig. 11. This figure shows the surface levels before and after a 10-minute etch at 80°C in a 5-1  $H_2O_2$ -NH<sub>4</sub>OH solution; in Fig. 12 levels for treatment in 5-1-1  $H_2O-H_2O_2$ -NH<sub>4</sub>F solution are displayed.

#### 7. Summary and Conclusions

Two sequential cleaning solutions  $(H_2O-H_2O_2-NH_4OH, and H_2O-H_2O_2-HCl)$  have been devised for cleaning silicon surfaces to reduce organic and inorganic contaminants to the very low levels required for silicon device fabrication.

The solutions do not attack either silicon or silicon dioxide as long as sufficient hydrogen peroxide is present. If the hydrogen peroxide is depleted or if gross fluoride ion contamination is present, etching can occur.

The hydrogen peroxide depletion rate and the concentration de-

Fig. 11—Surface profiles of n- and p-type silicon regions before and after etching in ammonium hydroxide (conditions: 1 vol 27%  $NH_4OH + 5$  vol  $H_2O$ , 10 min at 80°C).

Fig. 12—Surface profiles of n- and p-type silicon regions before and after etching in fluoride hydrogen peroxide etch (conditions: 1 vol 40 wt % NH<sub>4</sub>F + 1 vol 30% H<sub>2</sub>O<sub>2</sub> + 5 vol H<sub>2</sub>O, 10 min at 80°C). pendence of the silicon etch rate in depleted hydrogen peroxide solutions or in fluoride ion contaminated solutions have been determined and found safe for the recommended cleaning conditions.

The chemical effectiveness of these solutions has been demonstrated by water spray tests and radiotracer analyses. Moreover, the ability of the cleaning procedure to remove electrically active impurities has been verified using CVBT measurements on MOS capacitors.

#### Acknowledgments

The authors wish to thank A. Mayer for his helpful suggestions in the course of this work, and P. D. Gardner and J. A. Amick for their critical reviews of the manuscript.

#### References

<sup>1</sup> D. E. Koontz, C. O. Thomas, W. H. Craft, and I. Amron, "The Preparation of Ultraclean Electron-Tube Components by Chemical Etching," Sym. on Cleaning of ElectronIc Device Components and Materials. **ASTM, STP** No. 246, Am. Soc. Testing Mats., p. 136, 1959 <sup>2</sup> W. Kern, "Radiochemical Studies of Semiconductor Surface Contaminations-I. Adsorption of Reagent Components," RCA Review, Vol. 31, p. 207, June 1970. <sup>3</sup> W. Kern, "Radiochemical Studies of Semiconductor Surface Contamination-11. Adsorption of Trace Impurities by Silicon and Silica," RCA Review, Vol. 31, p. 234, June 1970. <sup>4</sup> RCA Semiconductor and Materials Div., "PEM on 2N1708 Silicon Planar Epitaxial Transistor," Quart. Reps. No. 1, 3, and 4, May 1, 1962-April 30, 1963; AD-36-039-SC-86729. <sup>5</sup> L. V. Gregor, "Solvent Induced Polarzation in MOS Devices," Abstr. No. 12, Electrochem. Soc. Mtg., Cleveland, Ohio, May 1966. <sup>6</sup>R. A. Sunshine, "A Contamination-induced Unstable OxIde Charge In MOS Structures," Recent News Paper presented at the Conf. on Physics of Failure Effects, Battell Memorial Inst., Columbus, Ohio, 1966. 7 S. R. Hofstein, "Tritium-Labeled Field-Induced Proton Transport In SiO<sub>2</sub> Films," Appl. Phys. Letters, Vol. 11, p. 95, 1 Aug. 1967. <sup>8</sup> E. H. Snow, A. S. Grove, B. E. Deal, and C. T. Sah, "Ion Transport Phenomena in Insulating Films," Jour. Appl. Phys., Vol. 36, p. 1664, May 1965. 9 K. O. Batsford and D. D. Thomas, "Defects In Vapor-Grown Silicon," Electrical Communic., Vol. 38, No. 3, p. 354, 1963. <sup>10</sup> A. Goetzberger and W. Shockley, "Metal Precipitates in Silicon p-n Junctions," Jour. Appl. Phys., Vol. 31, p. 1821, Oct. 1960. <sup>11</sup> W. M. Bullis, "Properties of Gold in Silicon," Solid-State Electronics, Vol. 9, p. 143, Feb. 1966. <sup>12</sup> J. R. Szedon and R. M. Handy, "Migration of Gold and Nickel lons in Thin Films of Silicon Dioxide," Physics of Fallure in Electronics, Vol. 5, p. 202; T. S. Shilliday and J. Vaccaro, Eds., AD 655 397, 1967. 13 D. O. Feder and D. E. Koontz, "Detection, Removal, and Control of Organic Contaminants in the Production of Electron Devices, "Symp. on Cleaning of Electronic Device Components and Materials, ASTM, STP No. 246, Am. Soc. Testing Mats., p. 40, 1959. 14 S. R. Hofstein, "Proton and Sodium Transport in SIO2 Films," IEEE Trans. on Electron Devices, Vol. ED-14, p. 749, Nov. 1967. 15 A. G. Revesz and K. H. Zaininger, "The Si-SiO2 Solid-Solid Interface System," RCA Review, Vol. 29, p. 22, March 1968. <sup>16</sup> W. C. Schumb, C. N. Satterfield, and R. L. Wentworth, Hydrogen Peroxide, Reinhold Publ. Corp., New York, N. Y., 1955. <sup>17</sup> D. B. Broughton, R. L. Wentworth, and M. E. Farnsworth, unpublished work of the M.I.T. Hydrogen PeroxIde Project, 1947.

18 V. Zotier, Bull. Soc. Chim., Vol. 13, p. 61, 1913; ibid., Vol. 21, p. 241, 1917.

19 A. Bach and M. Monosson, Ber., Vol. 57B, p. 735, 1924.

<sup>20</sup> O. Hahn, H. Gille, Z. Anorg. Allgem. Chem., Vol. 112, p. 283, 1920.

<sup>21</sup> G. Schluck, Monatsh., Vol. 37, p. 489, 1916.

<sup>22</sup> N. Goldsmith and W. Kern, "The Deposition of Vitreous Silicon Dioxide Films from Silane," RCA Review, Vol. 28, p. 153, March 1967.

<sup>23</sup> R. J. Archer, "Determination of the Properties of Films on Silicon by the Method of Ellipsometry," Jour. Opt. Soc. Amer., Vol. 52, p. 970, Sept. 1962.

<sup>24</sup> K. H. Zaininger and A. G. Revesz, "Ellipsometry—A Valuable Tool in Surface Research," RCA Review, Vol. 25, p. 85, March 1964.

$^{25}$  A. N. Saxena, "Use of an Ellipsometer to Determine Surface Cleanliness and Measurement of the Optical and Dlelectric Constants of InSb at X = 5461 Å," Appl. Phys. Letters, Vol. 7, p. 113, 1 Sept. 1965.

<sup>26</sup> A. N. Saxena, RCA, Private Communication.

27 A. Mayer, RCA, Private Communication.

<sup>28</sup> J. W. Faust, Jr., "Etching of Metals and Semiconductors," in H. C. Gatos, Surface Chemistry of Metals and Semiconductors, John Wiley and Sons, New York, N. Y. 1960, p. 151.

<sup>29</sup> R.P.S. Black and A. T. Hawkinson, "Chemical Factors in the Use and Handling of Electronic Grade Hydrogen Peroxide," Symp. on Cleaning and Materials Processing for Electronic and Space Apparatus ASTM STP No. 342, p. 87, 1962.

<sup>30</sup> "Standard Methods of Preparation of Metallographic Specimens," ASTM Publication No. E3-62.

<sup>31</sup> F. Rosenberg, Handbook of Electron Tube and Vacuum Techniques, Addison Wesley, p. 11, 1965.

3<sup>2</sup> R. Meddings and V. N. Makin, "The Gaseous Reduction of Metals from Aqueous Solution," Application of Fundamental Thermodynamics to Metallurgical Processes, p. 105, Gordon and Breach, New York, N. Y., 1967.

<sup>33</sup> J. Zuber, RCA, Private Communication.

<sup>34</sup> J. I. Carasso and M. M. Faktor, "Oxidation Reactions and Potentials of Ge and Si," Chap. 5, The Electrochemistry of Semiconductors, P. J. Holmes, Ed., Academic Press, New York, 1962.

<sup>35</sup> Research Triangle Institute, Integrated Silicon Device Technology, Vol. X, p. 149, Tech. Dept. ASD-TDR-63-316, 1965.

# Radiochemical Study of Semiconductor Surface Contamination

#### I. Adsorption of Reagent Components

#### Werner Kern

RCA Laboratories, Princeton, N. J.

Abstract—The adsorption of reagent components on semiconductor surfaces was measured by radioactive tracer methods to assess the extent of surface contamination from typical reagent solutions used in solid-state-device processing. Substrates used were primarily silicon and germanium. Reagent solutions include NaOH, HF, HCl, HF-HNO3-CH3CO2H mixtures, iodine-containing semiconductor etchants, and chromic-sulfuric acid. Radionuclides used as tracer ions are Na<sup>22</sup>, Na<sup>24</sup>, F<sup>18</sup>, Cl<sup>38</sup>, and I<sup>131</sup>.

Adsorption of Na<sup>+</sup> ions by Si slices from dilute NaOH at 25°C was predominantly physical, Si increasing slowly with increasing NaOH concentration. In 0.1% NaOH, adsorption equilibrium was established in 1 hour, leading to 4  $\times$  10<sup>13</sup> Na<sup>+</sup>/cm<sup>2</sup>. An initial 60-second rinsing treatment in cold H<sub>2</sub>O removed 63%, but continued rinsing desorbed Na<sup>+</sup> at decreasing rates. Hot water desorbed 99.5% within 2 minutes, lowering the surface concentration to below 0.004 monoionic layer.

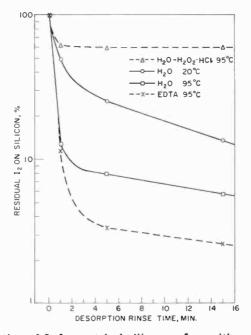

Etching of Si wafers in 5% NaOH at 100°C led to 1 × 1014 Na+/cm<sup>2</sup>. Desorption with HCI reduced this layer to less than 0.0002 of one monolayer of Na<sup>+</sup> ions. In contrast to thermal SiO<sub>2</sub>, pyrolytic SiO<sub>2</sub> sorbed large quantities of Na<sup>+</sup>, probably due to its porous nature. On immersing in diluted HF. Si and Ge wafers adsorbed on the order of 1016 to 1017 F-/cm2. The major portion was desorbable by rinsing with cold water, but a fluoride residue of several monolayers remained. Fluoride in Si volatilized only partly at 1250°C. Etching of Si and Ge wafers in strong HF-containing etchants led to concentrations in the 1016 F<sup>-</sup>/cm<sup>2</sup> range. Desorption of etched and water-rinsed wafers with acetone was extremely effective, reducing the adsorbate to a residual concentration of 1014 F-/cm2 in 30 seconds. Si etched in hot NaOH followed by immersion in dilute radioactive HCI adsorbed 1 × 1014 CI-/cm2. Ge immersed directly in the HCI acquired 3  $\times$  10<sup>14</sup> Cl<sup>-</sup>/cm<sup>2</sup>. Metal surfaces adsorbed larger quantities, especially indium (1017 CI-/cm2). lodine from CP-4 type etch mixture contaminated both Si and Ge surfaces with 1013 to 1014 l2 molecules/cm2. The adsorbate on Ge could be desorbed readily with aqueous solutions, but Si required hot EDTA solution to lower the residue to 3% of the initial value in 5 minutes. A special etch containing only 1.9 mg/liter Nal led to uniformly adsorbed 10<sup>11</sup> l<sub>2</sub>/cm<sup>2</sup> on Si and 10<sup>12</sup> l<sub>2</sub>/cm<sup>2</sup> on Ge. lodide ions from 1N Nal led to 1014 I<sup>-</sup> ions/cm<sup>2</sup> Si or SiO<sub>2</sub>. Treatments of Si in hot chromic-sulfuric acid, followed by cold water rinsing, resulted in absorbed chromium concentrations of less than 1014 atoms/cm2.

#### 1. Introduction

The electrical properties and the stability of semiconductor devices are strongly influenced by contaminants inadvertently introduced during the many processing steps required to fabricate the devices. Contaminants can originate from many sources—organic residues from photoresist polymers and solvents, gases or vapors from the ambient, and anions or cations from etch and rinse solutions. Of these contaminants inorganic ions are particularly detrimental to semiconductor devices.

The contamination of the semiconductor or oxide surfaces usually occurs as a result of physical or chemical adsorption, by electrolytic action, or by exchange of surface atoms with impurity ions in the solution. Some of the impurities deposited on the surface may be removed by suitable desorption treatments. Heating of oxide-coated semiconductor wafers at high temperatures during subsequent processing may cause diffusion of residual impurities to the oxide semiconductor interface. The extremely high fields that exist at p-n junctions during operation of the finished device can also give rise to surface migration of ionic impurities. The effects of these contaminants may become manifest in uncontrolled drifts of the semiconductor surface potential, changes in the minority-carrier lifetime at the surface, surface recombination velocity, and the formation of inversion or accumulation layers. These effects can lead to increased and erratic reverse leakage current in devices.

The effects on device performance of the following fast-diffusing contaminants have been studied extensively: gold,<sup>1,2</sup> copper,<sup>1,3-5</sup> iron,<sup>1,5</sup> manganese,<sup>1,6</sup> and sodium.<sup>7-9</sup>

Of the papers published concerning surface contamination from inorganic solutions, few discuss the situation under actual conditions of semiconductor device processing. Holmes and Newman employed electron diffraction to examine deposits on silicon and germanium surfaces etched in solutions to which various metals had been added.<sup>10</sup> Neutron-activation analysis was employed by Bemski and Struthers<sup>11</sup> and by Carlson<sup>12</sup> to detect gold on silicon. Several groups of workers determined sodium concentrations in silicon and silicon dioxide films by neutron-activation and radio-tracer techniques.<sup>9,13-18</sup> Radioactive tracers were also used by Larrabee<sup>19</sup> for measuring cationic impurity adsorption from solution on silicon surfaces, by Krembs and Schlacter<sup>20</sup> on germanium, and by Fowkes et al. on silicon,<sup>23, 24</sup> and silicon dioxide<sup>24</sup> surfaces has also been measured by tracer methods.

Contamination studies with compound semiconductors have been

reported by Larrabee<sup>25</sup> who employed radiotracers in solutions, and by Kern<sup>26</sup> who investigated contamination of gallium arsenide from quartz crucibles during synthesis by means of neutron activation and gammaray spectrometry.

Radiochemical contamination studies with metal components on which transistors are mounted were published in a previous paper.27 The results of the present work will therefore be confined primarily to semiconductor surfaces to assess surface contamination from solutions under conditions frequently encountered during device processing. This paper, Part I, describes contamination from reagent components; Parts II<sup>‡</sup> and III<sup>\*</sup>, will discuss contamination from trace impurities. Both acid and alkaline etch solutions of typical composition but "tagged" with radioactive tracers were used to measure the extent of deposition on the sample surfaces. Desorption data were analyzed to determine the mechanism and reversibility of impurity deposition.

#### 2. Experimental Methods

#### 2.1 Semiconductor and Silica Substrates

Variously doped silicon and germanium wafers cut from (111)-oriented single crystals were used. In a few instances, hyperpure silicon powder\*\*\* was used to increase the surface area, thus enhancing the analystical sensitivity. The wafers were either lapped, mechanically polished, or chemically polish-etched, as indicated in the tables. Before use, the wafers were degreased with hot organic solvents, nonionic surfactant solution, and finally rinsed with deionized and distilled water. Thermally grown or chemical-vapor-deposited silicon dioxide films, as well as plates of natural fused quartz\*\* were also used. Impurity concentrations in the latter were published previously.26

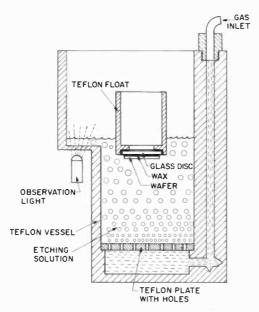

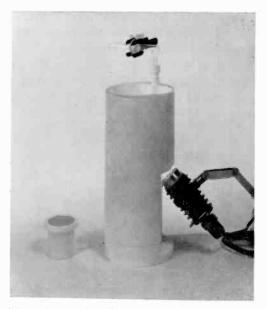

#### 2.2 Preparation of Radioactive Reagent Solutions

Pertinent nuclear data<sup>28</sup> of the radionuclides used as tracers are summarized in Table I. The isotopes and reagent solutions were prepared as follows :

Dilute radioactive sodium hydroxide containing Na<sup>22</sup> was prepared in our laboratory from carrier-free Na<sup>22</sup>Cl in HCl solution.<sup>†</sup> Curie-

<sup>&</sup>lt;sup>‡</sup> RCA Review, Vol. 31, p. 234, June 1970.

<sup>\*</sup> To be published in September 1970 issue of RCA Review.

<sup>\*\*\*</sup> Pigment Dept., E. I. DuPont de Nemours and Co. (Inc.), Wilmington 98, Del. \*\* Vitreosil, Trademark of Thermal American Fused Quartz Company. Distance and Engineering Corporation, Pittsburgh,

Pa.).

|                   |           |                      |                          |                               | Principle Radiations    | Radiations                 |                      |

|-------------------|-----------|----------------------|--------------------------|-------------------------------|-------------------------|----------------------------|----------------------|

| Isotope           | Lifetime  | Modes<br>of<br>Decay | Decay<br>Energy<br>(MeV) | Particle<br>Energies<br>(MeV) | Particle<br>Intensities | Gamma<br>Energies<br>(KeV) | Gamma<br>Intensities |

| nNa <sup>22</sup> | 2.602 y   | $\beta$ +, EC        | 2.84*                    | 0.54*<br>EC*                  | $89\% ^{*}_{*}$<br>11%  | AR<br>1275                 | * <b>%</b> 66        |

| "Na <sup>24</sup> | 15.0 hr   | β-                   | 5.51                     | 1.389                         | <i>%</i> + 66           | $\frac{1369}{2754}$        | 100%<br>100%         |

| »F18              | 109.7 min | $\beta^+, EC$        | 1.65                     | 0.635<br>EC                   | 97%<br>3%               | AR                         |                      |

| 17Cl38            | 37.3 min  | 8-                   | 4.91                     | 4.81<br>2.77<br>1.11          | 53% 16% 31%             | 1600<br>2168               | 85**<br>100          |

| 181 Isa           | 8.070 d   | β-                   | 0.970                    | 0.333<br>0.606                | 6.9%<br>90.4%           | 284<br>364<br>637          | 5.9%<br>79%<br>6.7%  |

Table 1-Pertinent Properties of the Radioactive Isotopes Used as Tracers

T

Data compiled from Ref. [28], except \* which are from the 45th Edition (1964). Notes:

$eta^- = \text{Negative beta emission}$  $eta^+ = \text{Positron emission}$ EC = Orbital electron capture $AR = 511 \, \text{KeV}$  photon associated with the annihilation of positrons in matter \*\* = Relative intensity  $Y = Y \, \text{ear}$ d = Day

level quantities of radio sodium were prepared<sup>††</sup> by thermal neutron activation of sodium hydroxide pellets by an ion-exchange treatment at a thermal neutron flux of  $2.5 \times 10^{13}$  n/cm<sup>2</sup> sec. The resulting Na<sup>24</sup>OH permitted the use of high specific radioactivities (curies per gram of sodium) with consequent increase in the analytical detection limit. Fluorine-18, prepared by reactions discussed previously,<sup>27</sup> was obtained in ionic form# in 0.1N NaOH with chloride ions as non-isotopic carrier. The prepurified solution was further refined by neutralizing with HF, concentrating by distillation, and passing through a Dowex-50 W-X8 cation exchange column in the H+ form to remove the sodium ions. The eluate was then mixed with appropriate quantities of 49% HF. Chlorine-38 was prepared by thermal neutron activation of pure calcium chloride.\* CaCl2 was chosen as target material because no interfering gamma radioactivity is generated from either the calcium or the chlorine by the thermal (n, p) activation, or by possible fast neutron reactions; 100 mC Cl<sup>38</sup> activity was generated and converted to 0.2N HCl by passing the radioactive CaCl<sub>2</sub><sup>38</sup> solution through a Dowex cation exchange column in the H+ form. Iodine-131 was obtained as carrier-free, high-purity NaI<sup>131</sup> solution.<sup>†</sup> Aliquots of the solution were added to standard iodine etch mixtures, yielding molecular iodine of the same chemical form as the normal iodine present in the etchants.

#### 2.3 Sample Exposures

The substrates were immersed in the radioactive reagents in polyethylene beakers, usually with slight agitation. In the case of the acid etch mixtures, the nominal temperature is the starting temperature, but the exothermic etching reactions usually increased the temperature by several degrees during use. Samples were withdrawn from the etch bath with plastic-coated tweezers, except when etching in mixtures containing HF and  $HNO_3$ ; here the etching was always terminated by rapidly diluting with deionized water.

#### 2.4 Initial Rinsing of Samples

Following removal of the wafers from the etch bath, a series of water rinses was applied to remove droplets of radioactive etch solution that

<sup>&</sup>lt;sup>††</sup> RCA nuclear reactor facilities at Industrial Reactor Laboratories, Inc., Plainsborough, N. J.

<sup>#</sup> Brookhaven National Laboratories, Upton, N. Y.

<sup>\*</sup> RCA nuclear reactor facilities at Industrial Reactor Laboratories, Inc., Plainsborough, N. J.

<sup>&</sup>lt;sup>†</sup>Oakridge National Laboratory, Oakridge, Tenn.

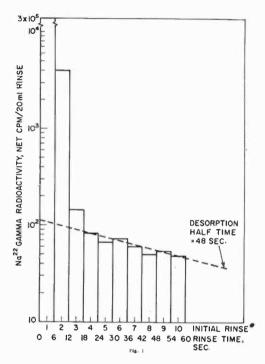

by the water rinses (minus drag-out) was 742 cpm, or 63% of the total Na+ initially present.

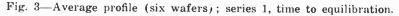

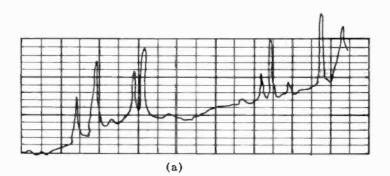

Fig. 1—Sodium-22 radioactivity in initial water rinses from Na<sup>22</sup>OHtreated silicon. 20 ml deionized  $H_2O$  per 6-second-rinse from lapped silicon wafers that had been immersed in 0.03N Na<sup>22</sup>OH at 25°C. Desorption half-time = 48 sec.

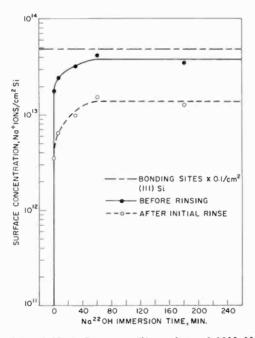

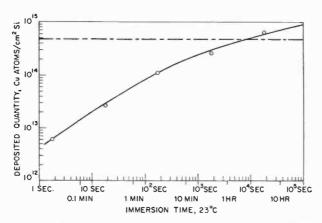

The initial concentrations of Na<sup>+</sup> adsorbed from 0.03N NaOH as a function of immersion time were measured by the above technique. The results, shown graphically in Fig. 2, indicate that adsorption equilibrium of  $3.8 \times 10^{13}$  Na<sup>+</sup>/cm<sup>2</sup> is attained in approximately 1 hour. Na<sup>+</sup> adsorption on mechanically polished<sup>\*</sup> wafers with a mirrorlike surface finish was only 30% lower than on lapped wafers, indicating that the true surface area of lapped wafers is reasonably close to their geometric area, as used in these calculations.

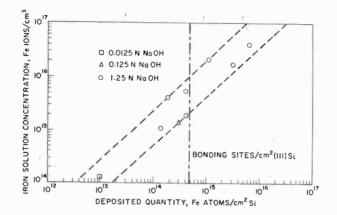

A limited number of data was obtained relating  $Na^+$  adsorption at 25°C to the NaOH concentration over the range 0.003 to 6N. The relation was found to follow a Freundlich-type adsorption isotherm. The quantity of adsorbed  $Na^+$  after the initial 60-second rinse sequence in-

<sup>\*</sup> Polished with Linde Type A-5175 abrasive powder and felt wheel.

creased approximately  $2\frac{1}{2}$ -fold for a 10-fold increase in the NaOH concentration.

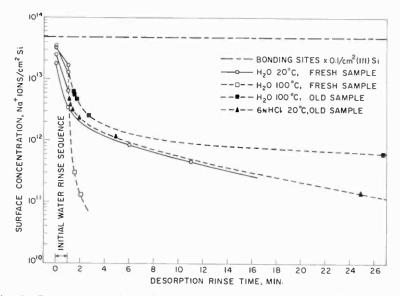

Desorption with water beyond the initial 60 seconds of rinsing continued to decrease the Na<sup>+</sup> surface concentration rather rapidly, as seen from the typical desorption curves in Fig. 3. Water at 100°C was particularly effective, decreasing the initial concentration 200-fold within 2 minutes to a residual Na<sup>+</sup> quantity corresponding to 0.004 monoionic layer. The ease of removal of Na<sup>+</sup> from silicon indicates predominantly physical adsorption.<sup>\*\*</sup>

Similarly, 6N (19%) HCl also removes Na<sup>+</sup> from a recently immersed surface at a much higher rate, as shown in the next section.

The importance of rinsing samples immediately following an etching treatment was demonstrated by the following experiment. Two

Fig. 2—Adsorption of Na+ Ions on silicon from 0.03N Na<sup>22</sup>OH at 25°C as a function of immersion time. Upper curve shows adsorbed Na+ prior to rinsing. Lower curve shows adsorbed Na+ after 60 sec initial water rinse sequence.

<sup>\*\*</sup> Since the substrate surface is covered with a thin layer of natural oxide, which in the presence of water will hydrate forming silanol groups  $(\sim 8 \times 10^{14} \text{ Si-OH/cm}^2)^{29}$  it can be expected that physical adsorption takes place primarily by electrostatic attraction of Na+ and Na+OH- ions to the electrically charged hydroxylated silicon surface forming an ionic double layer structure.

silicon wafers were immersed in 0.04N NaOH followed by the initial 60-second rinse sequence, but they were then stored in room air for several weeks before continuing the desorption with 100°C-water or with 6N HCl (Fig. 3). This resulted in a considerably lowered desorption rate compared to samples that were stored for less than 24 hours, probably due to the growth of a surface oxide that tends to trap impurity ions.

Fig. 3—Desorption of Na<sup>+</sup> Ions from silicon with  $H_2O$  and HCl. Silicon wafers that had been immersed in 0.025N Na<sup>22</sup>OH followed by immediate initial rinsing in  $H_2O$  for 60 sec. Some samples (open symbols) were then desorption-treated as indicated within 24 hr. Other samples (solid symbols) were desorption-treated after several weeks of storage leading to inhibited desorption.

#### 3.1.2 Adsorption of Na+ Ions on Silicon from Na<sup>24</sup>OH at 100°C

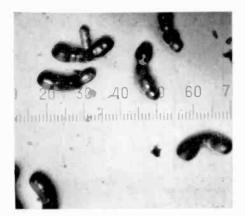

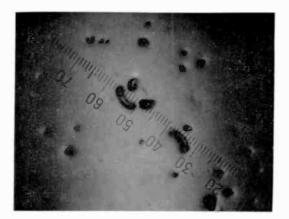

To assess sodium contamination during actual post-mount etching of silicon power transistors, various types of silicon wafers were prepared to simulate different doping and surface conditions. The wafers were etched for 60 seconds in 1.25N (5.0%) Na<sup>24</sup>OH at 95-100°C, followed by one of two special initial rinse treatments. These had been designed to simulate typical transistor processing conditions and to allow manipulation of the samples by remote control in the radiation hot cell. Initial rinse treatment "A" consisted of 3 immersions in cold deionized water for a total of 17 seconds in 330 ml per wafer to remove all of the "drag-out" from the etch bath without appreciably lowering the adsorbed Na<sup>+</sup>. In the alternative treatment "B", the etched wafers were immersed in 6N (19%) HCl for 15 seconds, using 60 ml per wafer; this was followed by 3 rinses in cold deionized water for a total of 15 seconds in 400 ml per wafer. All wafers were given a final dip in acetone to speed up drying in air. At this stage, the wafers were scanned with a Geiger-Mueller microprobe radiation detector that was connected to a counting rate meter to locate spots of high radioactivity. These sometimes occurred near the edge where the wafer was being held by the tweezers during the remote handling operations. Contaminated areas were carefully removed by scribing and breaking before accurate radioactivity measurement of the adsorbed Na<sup>24</sup> commenced. The results are summarized in Table II.

The adsorbed Na<sup>+</sup> concentrations of the water-rinsed series ("A") are 5 times lower on the heat-treated silicon wafers  $(3.4 \times 10^{13} \text{ Na}^+/\text{cm}^2)$  than on all the others, which average  $1.57 \times 10^{14} \text{ Na}^+/\text{cm}^2$ . The doping type, resistivity, and surface finish have no major influence on the quantity of Na<sup>+</sup> adsorbed.

Several additional etching and desorption experiments were conducted. Extending the etch time in the hot NaOH solution from 1 to 6 minutes did not increase the quantity of adsorbed Na<sup>+</sup> markedly, indicating that steady-state condition is established within the first minute of etching in hot caustic. This is reasonable, since silicon surface layers are continuously being removed by etching according to the equation

$$Si + 2NaOH + H_2O \rightarrow Na_2SiO_3 + 2H_2.$$

The initially water-rinsed silicon wafers were subjected to continued rinsing. Deionized water was used at a ratio of 1000 ml per wafer at a temperature of 20°C for rinse periods of 40 minutes. This additional water rinse descreased the Na<sup>+</sup> surface concentration listed in Table II to residual levels of about 10% of the value after the first water rinse ("A"). The sodium adsorbed on phosphorous-doped silicon required the entire 40 minutes of rinsing before it approached this concentration, whereas on boron-doped silicon this level was reached within 10 minutes. Representative desorption curves for each type are shown in Fig. 4. From this observation it appears that a phosphorus-doped silicon surface retains Na<sup>+</sup> more tenaciously than does one doped with boron.

The mean concentration on the initially acid-rinsed series ("B") was considerably lower:  $6.5 \times 10^{12}$  Na<sup>+</sup>/cm<sup>2</sup>. The average deviation

|          | A                   | Adsorbent Wafer         | jt                                                                                       | Adso                                                                    | Adsorbate                                                  |

|----------|---------------------|-------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|

| Dopant   | Resistivity<br>Type | Resistivity<br>(ohm-cm) | Preparation                                                                              | Na+ ions/cm <sup>2</sup><br>after H <sub>2</sub> O Initial<br>Rinse "A" | Na+ ions/cm <sup>2</sup><br>after HCl Initial<br>Rinse "B" |

| В        | d                   | 6.5-7.1                 | Lapped                                                                                   | $2.68 	imes 10^{14*}$                                                   |                                                            |

| В        | d                   | 6.5 - 7.1               | Mechanically Polished                                                                    | $1.38\times10^{14**}$                                                   | $1.00	imes10^{13}$                                         |

| в        | d                   | 6.5-7.1                 | Chemically etch-polished                                                                 | $1.83 	imes 10^{14}$                                                    | $0.62	imes10^{13}$                                         |

| В        | d                   | 6.5-7.1                 | Chemically etch-polished<br>and heated 21 hr at<br>1300°C; HF etched                     | $0.38 \times 10^{14}$                                                   | $0.21	imes10^{13}$                                         |

| В        | đ                   | 30†                     | Chemically etch-polished<br>and boron diffused 21<br>hr at 1300°C; HF<br>etched          | $0.36 	imes 10^{14}$                                                    | $0.55	imes10^{13}$                                         |

| <u>م</u> | c                   | 0.12†                   | Chemically etch-polished<br>and phosphorus dif-<br>fused 30 min at 1200°<br>C; HF etched | $0.29 	imes 10^{14}$                                                    | $0.83 \times 10^{13}$                                      |

| в        | d                   | 154                     | Lapped                                                                                   | $0.78	imes10^{14}$                                                      |                                                            |

| Ъ        | u                   | 1.3 - 3.5               | Lapped                                                                                   | $0.59	imes10^{14}$                                                      | $0.55	imes10^{13}$                                         |

| д.       | ч                   | 1.3-3.5                 | Mechanically polished                                                                    | $\sim 1.8 \times 10^{14}$                                               | $0.81 \times 10^{13}$                                      |

Table II-Adsorption of Sodium Ions on Silicon from Hot Sodium Hydroxide Solution (Na<sup>24</sup> Used as Radioactive

\* Average of 4 analyses, mean error  $\pm$  0.78  $\times$  10<sup>14</sup>

\*\* Average of 3 analyses, mean error  $\pm$  0.19  $\times$  10<sup>14</sup>

<sup>†</sup> Value in ohms/square.

Etching: 1 min in 1.25N (5.0%) NaOH at 95-100°C

1 immersion in 6N (19%) HCl at  $20^{\circ}$ C for 15 sec, 60 ml per wafer, followed by 3 immersions in deionized water at  $20^{\circ}$ C for a total of 15 sec and 400 ml per wafer. Initial Rinsing "A": 3 immersions in deionized water at 20°C for a total of 17 sec and a total of 330 ml per wafer. Initial Rinsing "B":

RADIOCHEMICAL STUDY I.

from this mean was only  $\pm 15\%$ , regardless of the type of silicon surface. The individual values were up to 30 times lower than on the corresponding water-rinsed samples, which demonstrates the excellent efficiency of aqueous HCl for desorbing Na<sup>+</sup> ions from silicon.

Fig. 4—Desorption of Na+ Ions from n-Type and p-Type Silicon with H<sub>2</sub>O Phosphorus and boron doped wafers etched in 1N Na<sup>24</sup>OH at 100°C. Initially rinsed with H<sub>2</sub>O (Table II); desorption rinsed with deionized H<sub>2</sub>O, 20°C; 100% value = Na+ surface concentration after initial water rinse.

It was readily possible to lower the residual Na<sup>+</sup> concentrations on the HCl-rinsed silicon wafers (Table II) still further by continued desorption treatment. A 5-minute immersion in an ultrasonically agitated water bath at 40°C lowered the Na<sup>+</sup> levels on the average nearly 10-fold to  $8 \times 10^{11}$  Na<sup>+</sup>/cm<sup>2</sup>. Alternatively, extending the HCl rinsing from 15 seconds to 2 minutes was even more effective, and resulted in a residual Na<sup>+</sup> concentration below  $5 \times 10^{11}$  Na<sup>+</sup>/cm<sup>2</sup>; this quantity represents less than 0.00014 monoionic layer of Na<sup>+</sup>. While this is indeed a small quantity of contaminant, it must be remembered that the resulting electronic effects can be significant. Attalla et al.<sup>30</sup> reported that 1/10,000th of one monolayer of ionic impurity is capable of inverting the surface of 1 ohm-cm silicon. The desorption treatments should therefore be as exhaustive as practically feasible.

RCA Review • June 1970 219

The desorption behavior suggests that the major portion of the sodium from hot NaOH is reversibly absorbed by electrostatic forces as noted in Section 3.1.1 for cold NaOH. However, a few percent appears to be strongly chemisorbed, requiring HCl or boiling  $H_2O$  for desorption. It is proposed that the chemisorption of sodium ions proceeds by exchange with the proton of the silanol group forming a  $\equiv$ Si-O-Na surface.

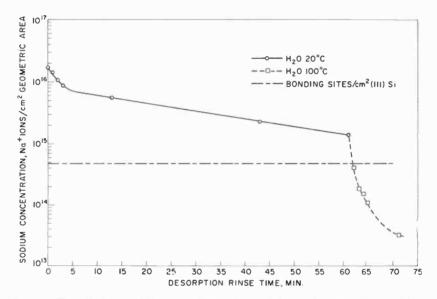

# 3.1.3 Adsorption of Na+Ions on Silicon Dioxide from Na<sup>22</sup>OH at 100°C

A comparative adsorption experiment with SiO<sub>2</sub>-coated silicon wafers was conducted by immersing the samples for 1 minute in NaOH (0.7N) at 100°C, followed by 60 seconds of water rinsing. Na<sup>22</sup> was the tracer in these tests. Thermally steam-grown SiO2 (1200°C, 1 micron thick film) retained less than  $3 \times 10^{13}$  Na<sup>+</sup>/cm<sup>2</sup>, whereas pyrolytically deposited SiO<sub>2</sub> (725°C, tetraethyl orthosilicate, 1 micron thick film)<sup>31</sup> retained  $1.4 \times 10^{16} \text{ Na}^+/\text{cm}^2$  geometric surface area. This large difference is probably due to the porosity of the undensified pyrolytic layer. Thermal SiO<sub>2</sub> and silicon immersed in cold NaCl solution are reported to have a much greater tendency of retaining Na+ ions than SiO<sub>2</sub> deposited from SiH<sub>4</sub> or SiCl<sub>4</sub>; however, in that work,<sup>18</sup> the Na+ was found trapped by localized surface defects (on the silicon wafer, or the oxide film) and could not be removed by water rinsing. This appears not to be the case in the present work, as shown in the water desorption curve (Fig. 5). The residual level detectable after 10 minutes rinsing in deionized water at 100°C was  $3 \times 10^{13}$  Na<sup>+</sup>/cm<sup>2</sup>, a decrease of nearly 1000-fold. The distribution of sodium in thermally grown silicon dioxide layers on silicon has been reported in considerable detail9, 13-18 and will not be discussed here.

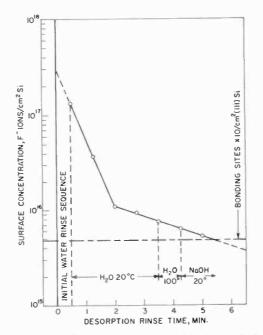

## 3.2 Fluoride lons from Hydrofluoric Acid Etchants

Five different etch compositions were prepared, all labeled with millicurie quantities of HF<sup>18</sup>. Silicon and germanium wafers of different doping types, resistivities, and surface finishes were immersed in the radioactive etchants at 25°C for periods ranging from 10 seconds to 6 hours. All samples were subjected to an initial water-rinse sequence prior to measuring the F<sup>18</sup> radioactivity: 5 rinses, each in 20 ml deionized water at 20°C for 6 seconds, followed by a dip in acetone for 6 seconds.

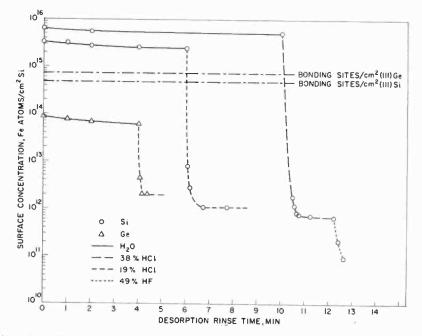

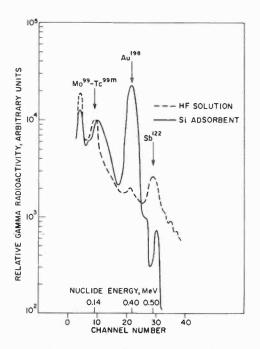

The rapid distintegration rate of  $F^{18}$  and the presence of small amounts of radioactive impurities made it difficult to perform the radioactivity measurements. The experimentally determined life-time for the resolved F<sup>18</sup> activity in the various etch solutions was within  $\pm 1.2\%$  of the theoretical, and the F<sup>18</sup> at the start of the measurements was 99.85% of the total gamma activity. The non-F<sup>18</sup> activity was identified by gamma spectrometry, decay analysis, and chromatographic colorimetric analysis as Sb<sup>122</sup>, Au<sup>198</sup>, and Mo<sup>99</sup>-Tc<sup>99m</sup>; their adsorption behavior will be discussed in Part II\* of this series. Electronic effects of adsorbed fluoride on silicon surfaces were described in the literature.<sup>32, 33</sup>

Fig. 5—Desorption of Na+ Ions from pyrolytic SiO<sub>2</sub> film with H<sub>2</sub>O. Silicon wafer coated with pyrolytic SiO<sub>2</sub> film immersed in 0.7N Na<sup>22</sup>OH at 100°C followed by the indicated rinsing treatments.

#### 3.2.1 Adsorption of F- Ions on Silicon from Aqueous HF<sup>18</sup>

Five silicon wafers, lapped on one side and mechanically polished on the other, that had been immersed 1N HF<sup>18</sup> for 30 minutes and rinsed for 30 seconds, retained 4.6 to  $7.7 \times 10^{16}$  F<sup>-</sup> ions/cm<sup>2</sup> regardless of the surface finish, the type of dopant, or the resistivity of the silicon. A summary of these and other data is presented in Table III. Diffusion doped wafers had 2 to 3 times higher concentrations for unknown reasons. A wafer freshly etched in HF-HNO<sub>3</sub> without F<sup>18</sup> tracer adsorbed

<sup>\*</sup> RCA Review, Vol. 31, p. 234, June 1970.

| Reagent                 |                        |                           | Adse                     | Adsorbant Wafer         |                                                                                          | Immersion          | Adsorbate             |

|-------------------------|------------------------|---------------------------|--------------------------|-------------------------|------------------------------------------------------------------------------------------|--------------------|-----------------------|

| Solution<br>Composition | Number<br>of<br>Wafers | Dopant                    | Resis-<br>tivity<br>Type | Resistivity<br>(ohm-cm) | Preparation                                                                              | Minutes<br>at 23°C | $F-ions/cm^{2*}$      |

| 1.1N HF                 | e                      | B                         | d                        | 4                       | lapped/polished                                                                          | 30                 | $6.46 	imes 10^{16}$  |

| 1.1N HF                 | 1                      | $\mathbf{S}_{\mathrm{b}}$ | u                        | 0.007                   | lapped/polished                                                                          | 30                 | $5.90 	imes 10^{16}$  |

| 1.1N HF                 | 1                      | р                         | đ                        | 160†                    | Chemically etch-polished<br>and heated 21 hr at<br>1300°C; HF etched                     | 30                 | $5.88 	imes 10^{16}$  |